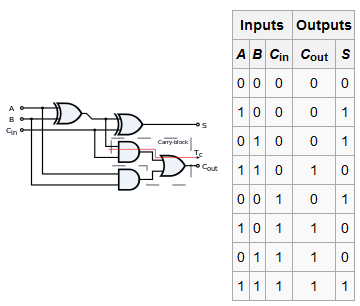

Setelah mempelajari dasar gerbang logika, fungsi logika PLC, rangkaian digital full adder, dan ladder diagram half adder, maka selanjutnya ialah mencoba menggabungkan implementasikan hal tersebut dalm ladder diagram full adder PLC. Sebuah full adder dapat dirangkai dari gabungan dua buah half adder. Ada dua buah output full adder yakni sum (Σ) dan carry (C), yang merupakan hasil dari beberapa input operand yang ada. Berikut ini ialah rangkaian digital full adder.

Dalam materi gerbang logika, telah dijelaskan bahwa gerbang logika AND hanya akan menghasilkan output bernilai 1, saat semua input bernilai 1. Bila ada satu saja input gerbang logika AND bernilai 0, maka output akan bernilai 0. Untuk operasi gerbang logika XOR, output akan bernilai 1 hanya pada saat nilai dari dua input yang ada berbeda. Dengan kata lain kedua input tidak boleh bernilai sama, apakah 1 dengan 1, atau 0 dengan 0, agar output yang dihasilkan bernilai 1. Untuk operasi gerbang logika OR, output akan bernilai 0 hanya pada saat nilai dari dua input yang ada ialah 0. Dengan kata lain untuk mendapatkan output bernilai 1, salah satu input (atau bahkan keduanya) harus bernilai 1.

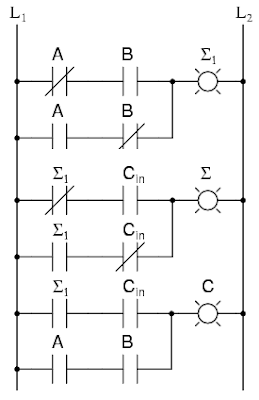

Langkah selanjutnya ialah menggabungkan fungsi logika PLC untuk AND, OR, dan XOR dalam satu ladder diagram. Hingga tersusun ladder diagram sebagai berikut.

Rangkaian full adder dapat disusun dari gabungan dua buah half adder. Untuk input dari full adder dalam ladder tersebut terdiri dari A, B, dan Cin. Dengan output Σ, Σ1, dan carry. Untuk Σ1 merupakan hasil operand XOR (antara input A dengan B) half adder pertama, Σ merupakan output sum akhir (dalam tabel kebenaran) yang mana merupakan hasil operand XOR (antara input Cin dengan Σ1), output carry merupakan hasil (A * B) + (Σ1 * Cin), dimana input A AND B dipadukan OR dengan Σ1 AND Cin.